您好,歡迎光臨帝國科技!

帝國博客

更多>>Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5-30+75

來源:http://ljnshy.cn 作者:康華爾電子 2024年05月21

Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5/-30+75

隨著處理器、多媒體和網絡技術的不斷進步,它們對帶寬的需求比以往任何時候都要大。點對點物理接口開始過時,因為它們很難跟上不斷增長的數據速率。為了繞過物理限制,已經利用共模邏輯來提供高速、低功耗的接口標準。

本技術說明旨在解釋和區分當今可用的主要邏輯接口:LVPECL;LVDS;HCSL;CML。

為什么選擇差分信號?

射頻電路中最大的問題之一是輸入波在傳輸過程中可能會被EMI失真,從而產生噪聲信號。

當信號通過單端連接傳輸時,石英振蕩子,傳輸過程中施加在其上的任何噪聲都會影響輸出,這可能會產生不可靠的失真波。

在差分信號中,兩條電線經常被扭曲在一起,成為EMI耦合,這意味著它們所經歷的干擾或多或少是相同的,使電線之間的電壓差幾乎為0V。這允許其中一根導線作為信號應該是什么樣子的參考,使輸出按預期輸出。

差分信號總體上比單端信號更不受噪聲影響。

LVPECL

低電壓正發射極耦合邏輯(LVPECL)最初是作為發射極耦合的邏輯(ECL)開始的。

ECL是早期的技術之一,它允許快速的開關速度,并且具有與CMOS相當的傳播時間

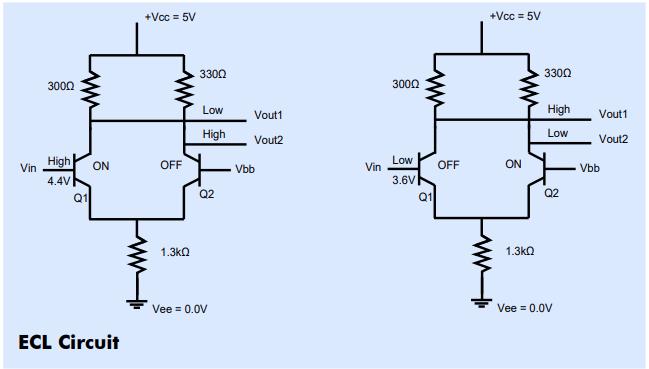

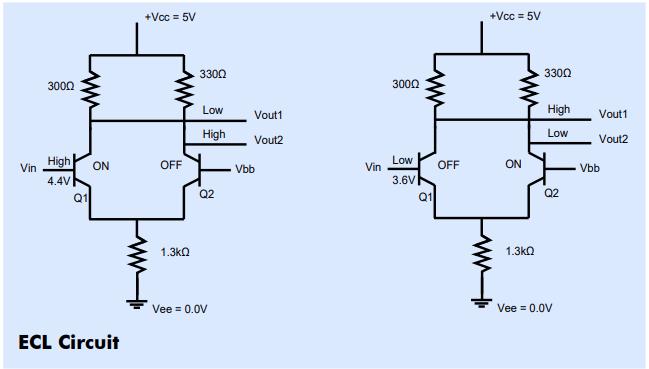

上圖所示的電路顯示了ECL接口的操作。

當“高”輸入通過Vin進入電路時,Q1導通,Q2截止。在此期間,Q1未飽和,這使Vout2變高,Vout1變低,因為壓降在300Ω以內。當“低”輸入通過Vin進入電路時,這種行為會得到反映。Q1將截止,Q2將導通,并且由于330Ω電阻器上的電壓下降,Vout1將為高,而Vout2將為低。

輸入高電壓和低電壓由電源電壓、基極電壓和發射極電壓值定義。在這個例子中,Vcc=5V,Vbb=4V和Vee=0V。這使得高和低的輸入值分別為4.4V和3.6V。

盡管ECL一直是一些應用程序中仍在使用的最流行的接口之一,但它也有缺點;低噪聲裕度、高功耗、電平移位器需要與其他邏輯門接口,最重要的是,它脫離負功率軌。這是有問題的,因為它使與其他邏輯族的接口變得困難,因為它們將負軌接地。最初使用負電源是因為它最大限度地減少了電源變化對柵極邏輯電平的影響。

這導致了正發射極耦合邏輯(PECL)的興起,進而導致了低壓正發射極耦聯邏輯(LVPECL)

這導致了正發射極耦合邏輯(PECL)的興起,進而導致了低壓正發射極耦聯邏輯(LVPECL)

進口晶振的ECL、PECL和LVPECL之間有什么區別嗎?

PECL和LVPECL使用正電源電壓,而ECL使用負電源。然而,這是唯一的主要區別,并且這三個接口都以相同的方式工作。

PECL允許使用5V正極電源,這簡化了電路的設計,并節省了少量的電力。

LVPECL現在是最常用的ECL接口,因為它保持了ECL的快速開關速度和低傳播時間,同時將電源電壓降低了約50%。

Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5/-30+75

Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5/-30+75

LVDS

低壓差分信號(LVDS)使用差分傳輸,這比單端方案具有巨大的優勢,因為它使其不太容易受到共模噪聲的影響。耦合到互連上的任何噪聲都被接收器視為共模調制,并被拒絕,這意味著接收器只對差分電壓做出響應。LVDS主要設計用于點對點應用,但總線LVDS(BLVDS)被定義為支持多點應用。

與ECL系列不同,LVDS不依賴于特定的電源電壓。這使得它在考慮電路設計的壽命時可以作為一個安全的選擇,因為它可以很容易地從5V遷移到3.3V或2.5V,同時仍然保持其性能。

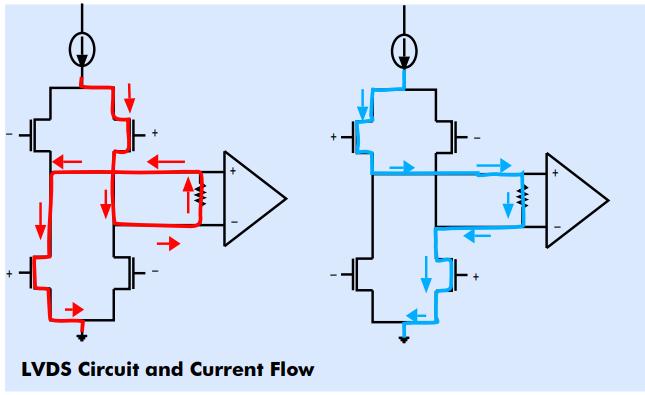

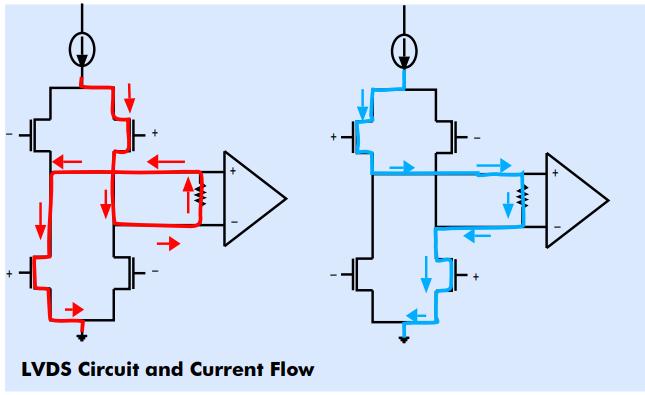

LVDS與其他邏輯接口不同,因為它不使用電壓波動,而是使用電流波動。它通過控制流經電路的電流的極性來工作。

LVDS與其他邏輯接口不同,因為它不使用電壓波動,而是使用電流波動。它通過控制流經電路的電流的極性來工作。

電流流經與線路阻抗匹配的電阻器(通常為100Ω),以避免高頻反射。當通過電阻器時,接收器輸入處會出現電壓降。接收器減去這兩個電壓以獲得差值。如果將3.5毫安的電流注入電路,并通過一個100Ω的電阻器,它將產生350毫伏的電壓(根據歐姆定律)。接收器能夠感測通過它的電流的極性以確定邏輯電平。

LVDS變送器消耗恒定電流,這大大減少了對電源去耦的需求,從而減少了對電路的電源和接地電平的干擾。

使用LVDS的優點是提高了電磁兼容性,并結合了低電壓操作。電壓順應性也加倍,因為信號不限于單端

輸出。

雖然LVDS石英晶振有它的優點,但它的抖動性能不如PECL,它更昂貴,并且在支持的最大數據速率方面受到限制。

LVDS最常見的用途是將數據從處理單元傳輸到顯示器。這主要包括以60Hz的刷新率將數據傳輸到LCD屏幕。它以前在計算機中用于從主板到顯示器的數據傳輸。盡管AMD和英特爾自2013年起停止支持LVDS,但它仍然廣泛用于電視和筆記本電腦。

Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5/-30+75

Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5/-30+75

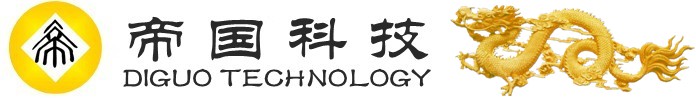

HCSL

高速電流導向邏輯(HCSL)是用于PCIe應用程序以及Intel芯片組的最受歡迎和支持的邏輯接口。

HCSL在低電流(通常為94mA,最大為115mA)下工作時產生的噪聲非常小。位于LVDS和LVPECL接口之間。這就是為什么它被選擇用于主板操作,因為它能夠產生清晰、無噪聲的信號。

HCSL的工作原理是將信號通過微分器,微分器會產生一個正波和一個負波。然后,這兩個波進入一個由電阻器端接的減法器。減法器放大信號的正部分,從而產生具有原始信號的兩倍振幅的輸出。

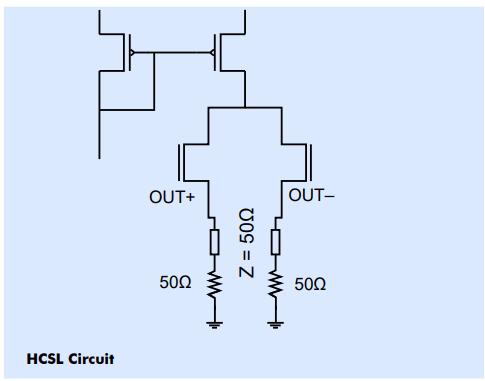

CML

共模邏輯(CML)是最簡單的高速邏輯接口之一。它提供低輸出電壓擺動,從而實現低功耗。

CML的工作原理是電流轉向。電流在兩個交替的路徑之間轉向。根據電流向下發送的路徑,它會在輸出處顯示“1”或“0”。

CML最常用于光纖元件,貼片晶振因為它在正確的端接下產生的噪聲非常小,并且能夠在印刷電路上傳輸大量數據(約312.5Mbit/s至3.125Gbit/s)

董事會。

正在載入評論數據...

此文關鍵字: 差分晶體振蕩器

相關資訊

- [2024-05-24]Bliley為您的設計尋找完美晶體振蕩器BOCS2-32.768KHZMBN-ABCT

- [2024-05-23]Jauch壓控溫補晶振O 10.0-JTS53HCV-F-K-3.3-1510-1015-LF適合在苛刻的環境中使用

- [2024-05-21]Euroquartz振蕩器差分輸出邏輯EMW576D33-155.52-2.5-30+75

- [2024-04-18]Fox推出FT1GNKUK26.0-T3溫補晶振提高性能

- [2024-04-13]Rakon用于先進無線電網絡的長期保持解決方案

- [2024-04-12]SiTime Endura低功耗SiT5543專用于國防領域

- [2024-04-12]SiTime解決了支持GPS的防御系統中的關鍵挑戰SiT7111

- [2024-04-11]Suntsu推出汽車晶體和振蕩器SAO22C3A4B1-30.000M

業務經理

業務經理